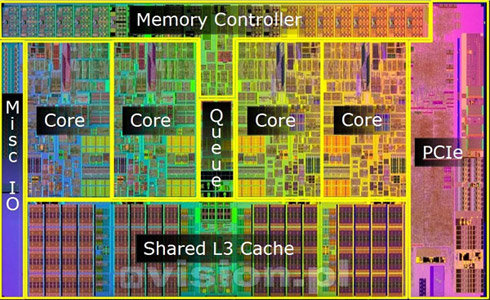

Już podczas premiery procesorów Core i5 750 byłem pod wrażeniem, że kontroler pamięci i kontroler PCI-e zostały przeniesione bezpośrednio do struktury procesora. Obok zdjęcie rdzenia Lynnfield z zaznaczonymi blokami funkcjonalnymi.

Już podczas premiery procesorów Core i5 750 byłem pod wrażeniem, że kontroler pamięci i kontroler PCI-e zostały przeniesione bezpośrednio do struktury procesora. Obok zdjęcie rdzenia Lynnfield z zaznaczonymi blokami funkcjonalnymi.

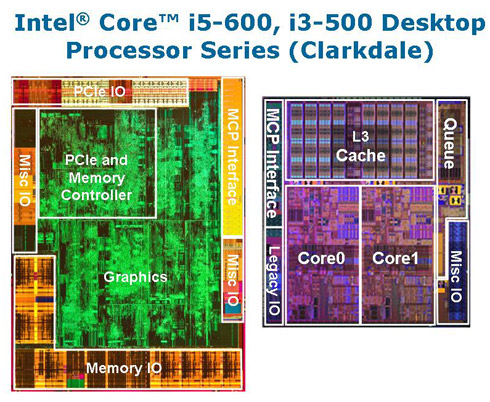

Nowe procesory Core i5 i Core i3 mają tę cechę rozwiązaną nieco inaczej. Będą konstrukcją wykonaną jako MCP, czyli Multi-chip Package, a nie w pełni zintegrowaną konstrukcją w jednym chipie.

Poniżej fotka ze zdjętym IHS. Widać wyraźnie dwie odrębne struktury.

Większa struktura po lewej stronie (obrazek po lewej), to wykonany w technologii 45nm mostek północny, który został w całości przeniesiony do opakowania procesora.

To właśnie tam znajduje się kontroler pamięci, kontroler PCI-e, oraz pozostałe kontrolery wejścia wyjścia. Nie zabrakło oczywiście interfejsu MCP do komunikacji z procesorem.

Kosteczka po prawej stronie, to 32nm rdzeń procesora Clarkdale, który komunikuje się w zasadzie głównie przez interfejs MCP.

Już od czasów premiery pierwszego Pentium D, a więc pierwszego chipa skonstruowanego w oparciu o MCP, w sieci nie gasną dyskusję na temat słuszności takiego rozwiązania. Czy mamy do czynienia z prawdziwym procesorem ze zintegrowanym kontrolerem pamięci?

Jednak dla przeciętnego użytkownika nie ma znaczenia, czy procesor wykonany jest jako MCP. Rozwiązanie zaprezentowanie przez Intela redukuje koszty nowej platformy, przez zmniejszenie ilości chipów, które potrzeba instalować na płytach głównych. Mniej chipów = tańsze płyty, co bezpośrednio przekłada się na większe zadowolenie klientów.

![30 proc. polskich konsumentów nie zamierza korzystać z zabezpieczeń biometrycznych [OPINIA]](http://cdn.benchmark.pl/thumbs/uploads/article/97727/MODERNICON/1f4c7dd778bbc8ea32d1dff9adebba22a18ee496.jpg/175x0x1.jpg)